1: Introduction

2 GP4020 GPS Baseband Processor Design Manual

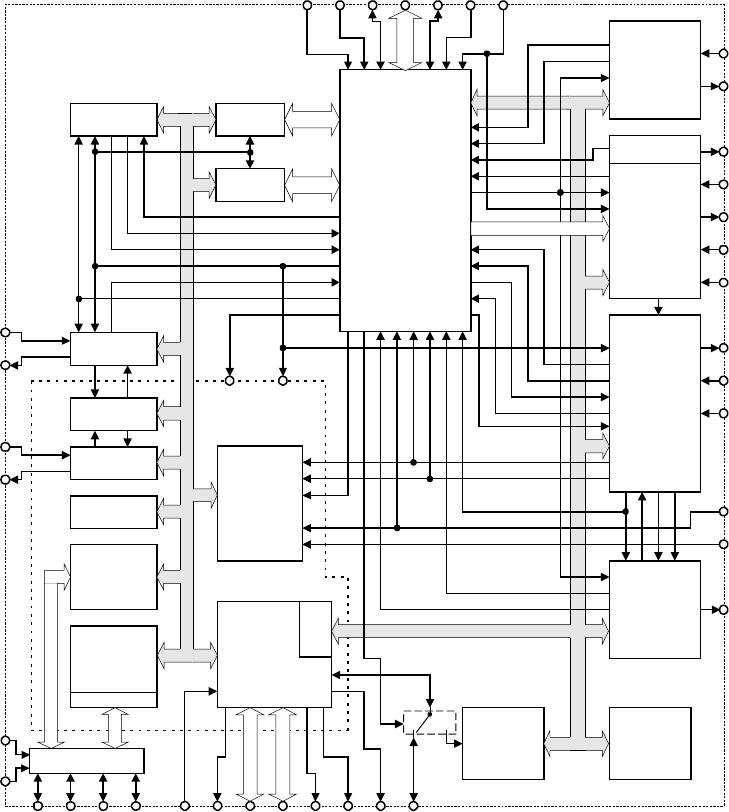

1.3 Functional Description

12 CHANNEL

GPS

CORRELATOR

RAM

(2k x 32)

MPC

UIM

ARM7TDMI

MICRO

JTAG

UART1

DMAC

TIC

SSM

INTC

Firefly

MF1 Core

SYSTEM

CLOCK

GENERATOR

UART2

BSIO

GPIO

PLL

BOOT

ROM

(512 x 16)

GPIO[7:0]

BSIO

U1RXD

U1TXD

GPIO[7:0]

U2TXD

U2RXD

SIGN0

MAG0

SAMPCLK

CLK_T

CLK_I

REAL

TIME

CLOCK

UIM BUS UIM BUS

UIM BUS

BuILD BUS BuILD BUS BuILD BUS

PR_XOUT

PR_XIN

M_CLK

BuILD_CLK

TESTMODE

RTC_XIN

RF_PLL_LOCK

IEXTINT2

1PPS

TIMEMARK

GENERATOR

TIMEMARK / TIC

RELOAD_TIC

TIC

PERIPHERAL

CONTROL

LOGIC

NRESET

UART_CLK

BuILD_CLK

UART_CLK

UART_INT

WATCH_INT

WATCH_EN

ACCUM_INT

MEAS_INT

NRESET

TIC_INT

PER_INT

NSRESET

DISCIO

RTC_XOUT

GPIO[7:0]

WATCH_TM

GP4020

NRESET

SDATA[15:0]

SWAIT

NSCS[2:1]

NSCS[0]

SADD[19:0]

SADD[19:0]

NSWE[1:0]

NSOE

NSUB

RAW

TIMEMARK

CK100KHz

DISCOP

JTAG INTERFACE

JTAG

NRESET

UART_CLK

NRESET

PLLDT1

PLLAT1

RTC_CLK

RTC_CMP_INT

M_CLK

TIMEMARK

TIMEMARK

RF_PLL_LOCK

NPOR_RESET

NPOR_

RESET

MULTI_FNIO

TIC

TEST

POWER_GOOD

SIGN0 / MAG0

SIGN1 / MAG1

POWER CONTROL LINES

INT_NCS0

TIC_INT

DISCIO /

DISCIP1

TEST

SSM BDIAG / XPIN IO

TCK

TDI

TDO

TMS

NICE

NTRST

NSCS[0]

SDATA[15:0]

MEAS_INT

ACCUM_INT

NRESET

DREQ2

DACK

DACK2

DREQ

WDOG

Figure 1.1 GP4020 Block Diagram

The GP4020 is a complete baseband processor for Navstar GPS C/A code signals. It incorporates a 12-channel

GPS correlator, a Zarlink Firefly MF1 micro-controller core (incorporating the ARM7TDMI Thumb microprocessor),

Real time Clock, 8k bytes of on-chip SRAM and a boot ROM. The GP4020 uses a fully configurable memory

interface, allowing the use of both 8-bit and 16-bit external memory. A Block Diagram of the GP4020 appears in

Figure 1.1 GP4020 Block Diagram" above.