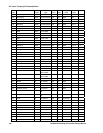

20: Input / Output pin Characteristics

186 GP4020 GPS Baseband Processor Design Manual

Pin

No.

Pin Name Pin

Type

IP / OP Cell

Type

5V

Tol.?

Hold

Cell?

Pull-up/ -

down

Tri-

state

Notes

34 SDATA[12] IP/OP CLAIO1HD03N No Yes None Yes

35 SDATA[13] IP/OP CLAIO1HD03N No Yes None Yes

36 SDATA[14] IP/OP CLAIO1HD03N No Yes None Yes

37 SDATA[15] IP/OP CLAIO1HD03N No Yes None Yes

38 SADD[18] IP/OP CLAIO1HD03N No Yes None

Note 3 2, 3

39 SADD[17] IP/OP CLAIO1HD03N No Yes None

Note 3 2, 3

40 SADD[16] IP/OP CLAIO1HD03N No Yes None

Note 3 2, 3

41 GND PWR CLALLGND

42 SADD[15] IP/OP CLAIO1HD03N No Yes None

Note 3 2, 3

43 SADD[14] IP/OP CLAIO1HD03N No Yes None

Note 3 2, 3

44 VDD PWR CLALLVDD

45 SADD[13] IP/OP CLAIO1HD03N No Yes None

Note 3 2, 3

46 SADD[12] IP/OP CLAIO1HD03N No Yes None

Note 3 2, 3

47 SADD[11] IP/OP CLAIO1HD03N No Yes None

Note 3 2, 3

48 SADD[10] IP/OP CLAIO1HD03N No Yes None

Note 3

2, 3

49 SADD[9] IP/OP CLAIO1HD03N No Yes None

Note 3

2, 3

50 SADD[8] IP/OP CLAIO1HD03N No Yes None

Note 3

2, 3

51 SWAIT IP CLAIP1GD No No 100k down -

52 NSUB OP CLAOP03N No - - Yes

53 IEXTINT2 IP CLAIP1NR No No None -

54 MULTI_FNIO IP/OP CLAIO1NR01N No No None Yes

55 DISCIO IP/OP SCJIO1NR01N Yes No None Yes

56 RF_PLL_LOCK IP CLAIP1NR No No None -

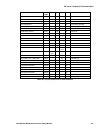

57 A1VDD PWR CLPLAN1VP

58 CLK_T IP

CLHANPIP to

SCLVDSRX

59 CLK_I IP CLHANPIP to

SCLVDSRX

60 GND PWR CLALLVM

61 SIGN0 IP CLAIP1NR No No None -

62 MAG0 IP CLAIP1NR No No None -

63 SAMPCLK OP CLAOP01N No - - No

64 POWER_GOOD IP CLAIP1NR No No None -

65 PR_XOUT CLGOSC1016

M

66 PR_XIN

CLGOSC1016

M

67 TEST IP CLAIP1GD No No 100k down -

68 VDD PWR CLALLVP

69 TIMEMARK OP CLAOP01L1 No - - No

70 IDDQTEST IP CLHIDDQ No No 100k down -

71 GND PWR CLALLVM

72 RTC_XIN CLGOSC32K

73 RTC_XOUT CLGOSC32K

74 TESTMODE IP CLAIP1NR No No None -

75 NSRESET IP CLAIP1NR No No None -

76 U2TXD OP CLAOP03L1 - - - No