18: Watchdog Timer

180 GP4020 GPS Baseband Processor Design Manual

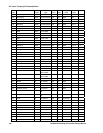

18.3.4

Watchdog Restart Register - RESTART - Memory Offset 0x00C

Bit

No.

Mnemonic Description Reset Value R/W

31: 0

RESTART _KEY

Restart Key. A write to this register with the correct key value,

0xECD9F7BD, restarts the WDOG primary counter.

0x00000000 W

Table 18.5 Watchdog RESTART Register

18.3.5

Watchdog TEST Register - TEST - Memory Offset 0x010

This register is only accessible when the GP4020 is put into TEST mode (i.e. ‘TEST’ (pin 67 (100-pin package)) is

set to Logic ‘1’, and ‘TESTMODE’ (pin 74 (100-pin package)) is set to Logic ‘0’).

Bit

No.

Mnemonic Description Reset

Value

R/W

31:21

Reserved

20 T_RST Replace reset signal ’slave_reset’ in TEST mode. 0 R

19 T_CLK Replace clock signal ’wd_clk’ in TEST mode. 0 R

18 T_EN Replace enable signal ’wd_en’ in TEST mode. 0 R

17 T_INT Current interrupt signal ’wd_int’. 0 R

16 T_TOUT Current time-out signal ’wd_tout’ 0 R

15:12

Reserved

11:0 SC_READ Current secondary counter read value 0 R

Table 18.6 Watchdog TEST Register

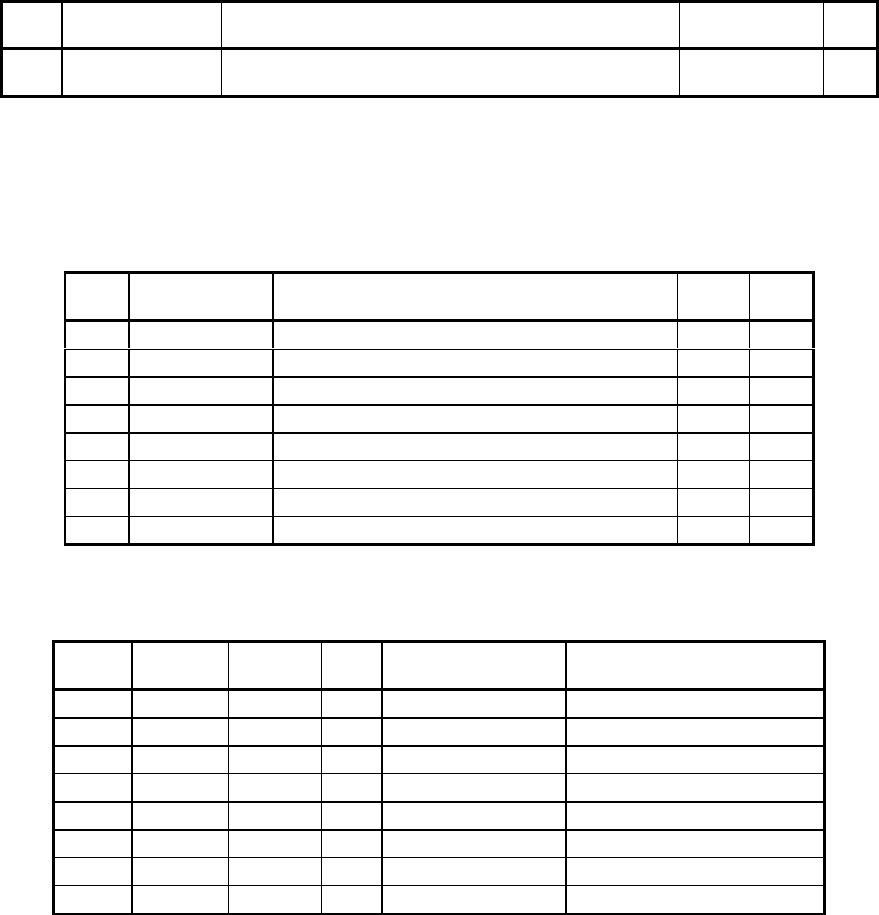

The relationship between the test signals and the external signals are shown in Table 18.7 below.

Test

mode

External

signal

Test

signal

IO Origin Destination

0 wd_clk -- I extern Primary/Secondary Counters

1 -- t_clk I test register Primary/Secondary Counters

0 wd_en -- I extern Primary Counter

1 -- t_en I test register Primary Counter

0 wd_int -- O Primary Counter extern

1 -- t_int O Primary Counter test register

0 wd_tout -- O Secondary Counter extern

1 -- t_tout O Secondary Counter test register

Table 18.7 Watchdog test signals