6: BSIO Interface

GP4020 GPS Baseband Processor Design Manual 43

SHIFT

CLOCKS

rx_clk

tx_clk

shift_rx

shift_tx

sclkx2

RWPOL

SSEL

WRITE

COUNTERS

TXWORD WRSIZE

shift_tx

end_of_tx

OPERATION

sclk_int

wfifo_wr

OPERATION

end_readtri_state_en

SCLK

And

Ext

Select

sclk_en

ext_sel

SSLEAD

SSLAG

OPERATION

sclkx2

end_write

SELBYTE

cword_en

CWORD

CWORDSEL

end_write

cword_wr

READ

COUNTERS

RXWORD RDSIZE

shift_rx

end_of_rx

end_write

sclk_int

VALBYTES

end_read

SELBYTE

SSEL

CYCDELAY

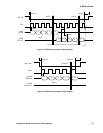

Figure 6.11 BSIO Sequencer

The Write Counters consist of a 5-bit binary counter to count the bit position within the currently transmitted control

or data word. There is also a 10-bit binary down counter. This is used to count the number of data words that

remain to be transmitted. At the start of an operation the counters are loaded with values determined by TXWORD

/ CWORD and WRSIZE in the Transfer and Mode Registers. After all the valid bits that make up a 32-bit word in

the Write FIFO have been shifted, the signal End_Of_Tx is asserted. End_Write is used to start the Read Counter,

after the last bit to be transmitted in the current operation has been shifted out of the Transmit Shift Register. When

the SELBYTE bit in the Transfer Register is set only byte-wide operations occur. If the CWORDSEL bit in the

Mode Register selects Page mode, the first word to be sent is the Control Word.

CWORD_EN acts as the shift enable signal for the Control Word Register, with CWORD in the Mode Register

selecting the width of the Control Word.

The Read Counters also consist of a 5-bit binary counter to count the bit position within the currently received data

word. Another 10-bit binary down counter counts the number of data words that remain to be received. At the start

of an operation, the counters are loaded with values determined by RXWORD and RDSIZE in the Transfer

Register. End_write, a signal from the Write Counter, is used to start the Read Counter, with CYCDELAY and

SSEL being able to select a 1 cycle delay for either SS0 or SS1. Shift_Rx, the control signal to the Read Buffer is

asserted when the first bit is to be read and de-asserted after the last bit has been shifted into the Receive shift

register. After all the valid bits that make up a 32-bit word in the RX FIFO have been shifted in, End_Of_Rx is

asserted, with end_read indicating the end of a complete read operation. The two status bits VALBYTES indicate

the number of bytes received. When the SELBYTE bit in the Transfer Register is set, only byte wide operations

occur.

The Operation bit in the Status Register is set when:

• the first word in an operation is written to the Write Buffer in Standard Mode,

• the Control Word is written in Page Mode.

The bit is cleared after the last bit of the current operation has been sent or received.