6: BSIO Interface

40 GP4020 GPS Baseband Processor Design Manual

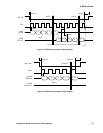

SSEL

OPERATION

SS0 - SS1

SCLK_INT

01H

00H 02H 03H 03H

00H

Note: ENPOL = 0000

Enable

Slave

Enable

Slave

Enable

Slave

Enable

Slave

Figure 6.7 BSIO SCLK Polarity Timing

SCLKON in the Configuration Register allows SCLK_INT to be stopped during an Operation.

6.4 BSIO Slave Select Logic

The Slave Select Logic, as shown in Figure 6.8 below, provides the Slave enable signals. When a Slave device is

to be selected, the Sequencer enables the Slave Select Logic by means of the ext_sel signal.

The SSEL bits in the Configuration Register will select either SS0_OP or SS1_OP as shown in Table 6.1 below:

SSEL OP

000 SS0

001 SS1

010 Reserved

011 Reserved

100 Reserved

101 Reserved

110 Reserved

111 Reserved

Table 6.1 BSIO Slave Select Enable Configuration

In addition the ENPOL bits in the Slave Select Registers, configure the polarity of their corresponding select outputs

(i.e. active High or active Low), with ENPOL = '0' selecting an active Low.

SLAVE

SELECT

LOGIC

SSEL

ENPOL

ext_sel

SS0_OP - SS1_OP

Figure 6.8 BSIO Slave Select Logic