7: 12-Channel Correlator

GP4020 GPS Baseband Processor Design Manual 69

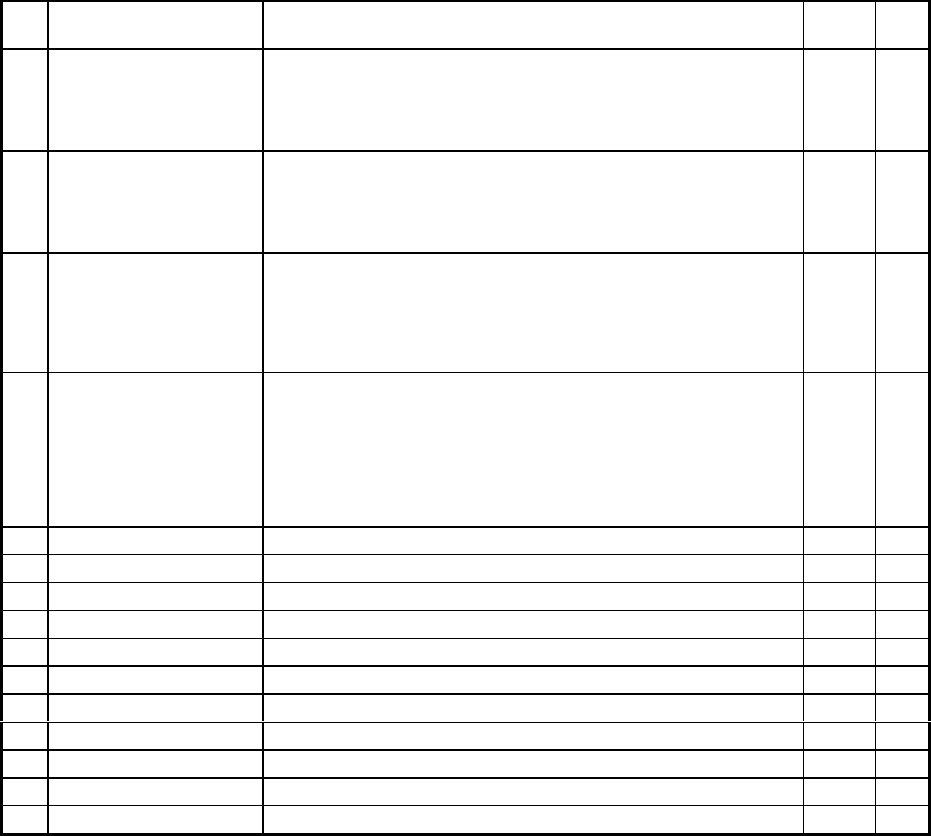

Bit

No

Mnemonic Description Reset

Value

R/W

14 DISCIP1

The DISCIP1 bit indicates the level on the DISCIP input pin at the time

this read occurs. It may be used to interface a hardware condition (such

as a ready flag from a UART, or the PLL LOCK signal from a front–end)

to the microprocessor without using an interrupt. This bit is not reset by a

hardware master reset nor by an MRB.

0R

13 TIC Set HIGH at every occurrence of TIC and is cleared by reading this

ACCUM_STATUS_B register. This bit can be used as a flag to the

microprocessor, to time software module swapping. It is reset by a

hardware master reset (NRESET at Low) but not by an MRB in

RESET_CONTROL.

0R

12 MEAS_INT

Provided that interrupts are enabled, the MEAS_INT bit is set High at

each TIC and 50 ms before each TIC (if the TIC period is greater then 50

ms), and is cleared by reading this register. This bit can be used to tell

the microprocessor that new Measurement Data is available. It is reset

by a hardware master reset (NRESET at Low), but not by a software

reset.

0R

11 CH11_MISSED_ ACCUM '1' = missed Accumulated Data due to a new DUMP in CHx before the

previous data has been read.

'0' = no missed data.

This bit is latched until the associated CHx_ACCUM_RESET is written

to. The data is sampled and latched on the active edge of every

ACCUM_INT signal and on request by performing a write operation to

STATUS (as with ACCUM_STATUS_A).

0R

10 CH10_MISSED_ ACCUM (as bit 11 but for channel 10) 0 R

9 CH9_MISSED_ACCUM (as bit 11 but for channel 9) 0 R

8 CH8_MISSED_ACCUM (as bit 11 but for channel 8) 0 R

7 CH7_MISSED_ACCUM (as bit 11 but for channel 7) 0 R

6 CH6_MISSED_ACCUM (as bit 11 but for channel 6) 0 R

5 CH5_MISSED_ACCUM (as bit 11 but for channel 5) 0 R

4 CH4_MISSED_ACCUM (as bit 11 but for channel 4) 0 R

3 CH3_MISSED_ACCUM (as bit 11 but for channel 3) 0 R

2 CH2_MISSED_ACCUM (as bit 11 but for channel 2) 0 R

1 CH1_MISSED_ACCUM (as bit 11 but for channel 1) 0 R

0 CH0_MISSED_ACCUM (as bit 11 but for channel 0) 0 R

Table 7.7 CORR ACCUM_STATUS_B Register

Note. If any accumulation data is missed due to the reading process being too slow this must be allowed for in the

software, such as by checking the Navigation Message data bit transitions independently of the sets of

Accumulated Data reads. If too much data is lost the system signal-to-noise ratio will be degraded. The primary

purpose of these bits is as a check on how well the tracking routines are working – once the whole design is

complete, these bits should not become set.

Channel specific bits of this register will not show their new value until after an active edge of ACCUM_INT or a

write to the STATUS register. Disabling a channel will however, clear the bit immediately.