6: BSIO Interface

GP4020 GPS Baseband Processor Design Manual 47

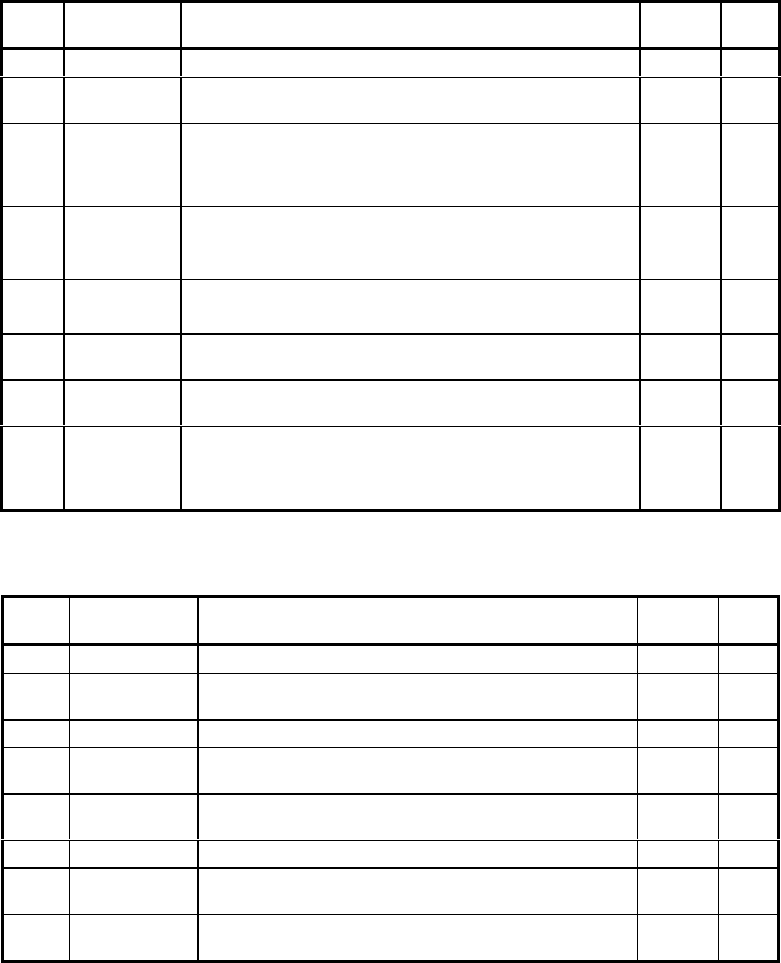

6.9.5 BSIO Status Register - BSIO_STAT - Memory Offset - 0x0030

Bit

No.

Mnemonic Description Reset

Value

R/W

31:8

Reserved

All = 0 R

7OPCOMP

Operation Complete: Set once current operation has

completed. Cleared by Read of Status Reg.

0R

6 OPERATION Operation: Set at start of operation, by first word written to

Write Buffer in Standard Mode or by writing the Control Word

in Page Mode. Cleared at end of operation after last word

sent or received.

0R

5 WRITERR Write Error: Set when an under-flow occurs in the Write

Buffer.

Cleared by Read of Status Register

0R

4 READERR Read Error. Set when an overflow occurs in the Read Buffer.

Cleared by read of Status Register.

0R

3:2 VALBYTES Valid Bytes. Number of Valid bytes to be read, from the Read

Buffer.

00 R

1 RDREADY Read Buffer Ready. Set when Read buffer contains at least

one valid word. Cleared when buffer is empty.

0R

0 WRREADY

Write Buffer Ready. Sets whenever the Write Buffer is ready

to store next 32-bit word, and more words are required to

complete the current transmit operation. Cleared when buffer

is full or all words have been transmitted.

0R

Table 6.7 BSIO Status Register

6.9.6 BSIO Interrupt Control Register - INTC - Memory Offset - 0x0034

Bit

No.

Mnemonic Description Reset

Value

R/W

31:8 -

Reserved

All = 0 R

7 OPCOMPEN Operation Complete Enable. Active High interrupt Enable

for the OPCOMP bit in the Status Register.

0R

6-

Reserved

0R

5 WRITERREN Write Error Enable. Active High Interrupt Enable for the

WRITERR bit in the Status Register

0R/W

4 READERREN Read Error Enable. Active High Interrupt Enable for the

READERR bit in the Status Register

0R/W

3:2

Reserved

00 R

1 RDREADYEN Read Ready Enable. Active High Interrupt Enable for the

RDREADY bit in the Status Register

0R/W

0 WRREADYEN Write Ready Enable. Active High Interrupt Enable for the

WRREADY bit in the Status Register

0R/W

Table 6.8 BSIO Interrupt Control Register