3: ARM7TDMI

TM

Microprocessor

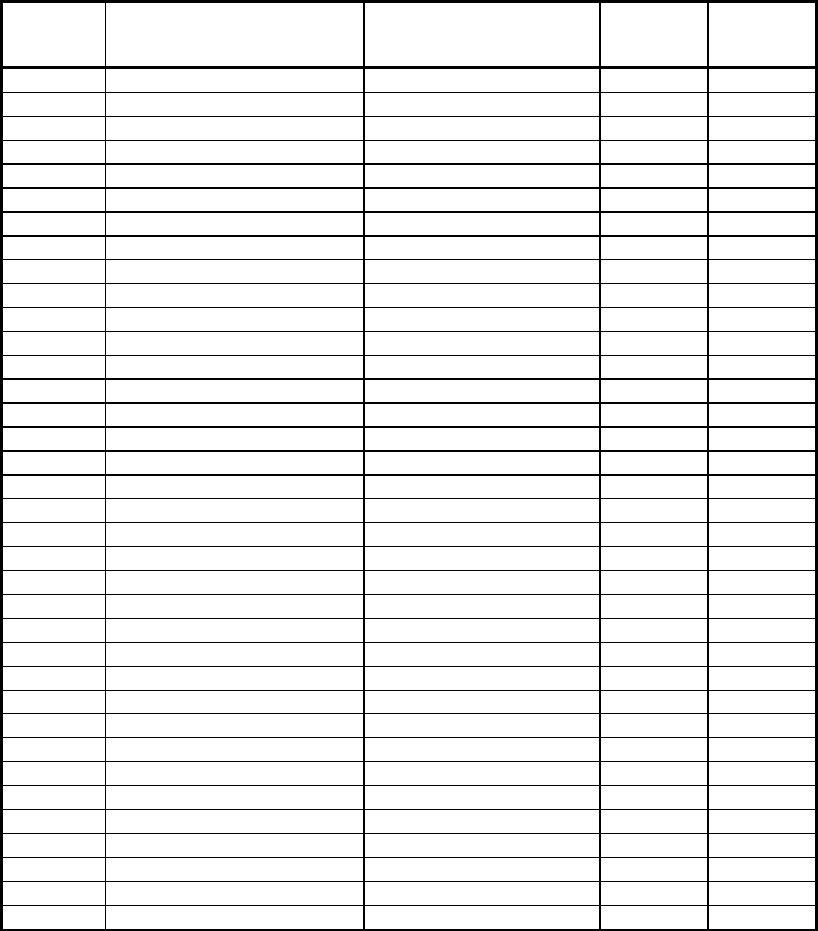

22 GP4020 GPS Baseband Processor Design Manual

Mnemonic Instruction Action Lo/Hi

register

operands

Condition

codes set

ADC Add with Carry Rd := Rd + Rs + C Lo Yes

ADD Add Rd := Rn + Rs Lo/Hi Yes*

AND AND Rd := Rd AND Rs Lo Yes

ASR Arithmetic Shift Right Rd := Rd ASR Rs Lo Yes

B Unconditional branch PC := PC +/- Offset11 Lo

Bxx Conditional branch PC := PC +/- Offset8 Lo

BIC Bit Clear Rd := Rd AND NOT Rs Lo Yes

BL Branch and Link PC := PC +/- Offset LR:=PC + 2

BX Branch and Exchange PC := Rs Lo / Hi

CMN Compare Negative Rd + Rs Lo Yes

CMP Compare CPSR flags :=Rd - Rs Lo / Hi Yes

EOR EOR Rd := Rd EOR Rs Lo Yes

LDMIA Load multiple Stack manipulation (Pop) Lo

LDR Load word Rd32 := [Rb + Immediate5] Lo

LDRB Load byte Rd8 := [Rb + Immediate5] Lo

LDRH Load half-word Rd16 := [Rb + Immediate5] Lo

LSL Logical Shift Left Rd := Rd << Rs Lo Yes

LDSB Load sign-extended byte Rd8 := [Rb + Immediate5] Lo

LDSH Load sign-extended half-word Rd16 := [Rb + Immediate5] Lo

LSR Logical Shift Right Rd := Rd >> Rs Lo Yes

MOV Move register Rd := Immediate8 Lo / Hi Yes*

MUL Multiply Rd := Rs * Rd Lo Yes

MVN Move Negative register Rd := NOT Rs Lo Yes

NEG Negate Rd := -Rs Lo Yes

ORR OR Rd := Rd OR Rs Lo Yes

POP Pop registers [SP] ++ := Rlist (LR) Lo

PUSH Push registers Rlist (LR):= [SP] -- Lo

ROR Rotate Right Rd := Rd ROR Rs Lo Yes

SBC Subtract with Carry Rd := Rd -Rs - NOT C Lo Yes

STMIA Store Multiple [Rb]++ := Rlist Lo

STR Store word [Rb + Immediate5] := Rd32 Lo

STRB Store byte [Rb + Immediate5] := Rd8 Lo

STRH Store half-word [Rb + Immediate5] := Rd16 Lo

SWI Software Interrupt OS call

SUB Subtract Rd := Rd - Immediate8 Lo Yes

TST Test bits CPSR flags :=Rd AND Rs Lo Yes

Table 3.2 16-bit Thumb instruction set

3.4 Operating Modes

ARM7TDMI supports seven modes of operation:

• User (usr) The normal ARM program execution state

• FIQ (fiq) Designed to support a data transfer or channel process

• IRQ (irq) Used for general-purpose interrupt handling

• Supervisor (svc) Protected mode for the operating system

• Abort mode (abt) Entered after a data or instruction pre-fetch abort