15: 1PPS Timemark Generator

166 GP4020 GPS Baseband Processor Design Manual

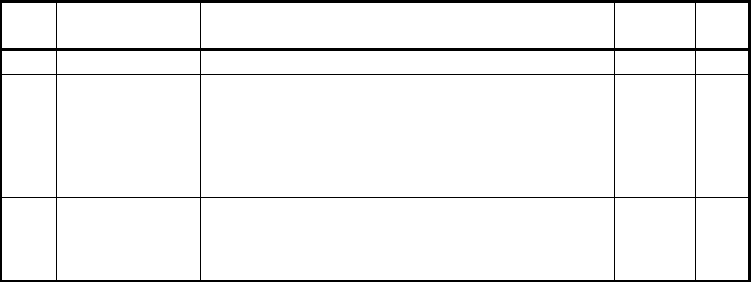

15.7.4 1PPS Timemark Generator Delay Counter Register (MSB) - TIM_DEL_HI - Memory Offset

0x016

This register sets the six most significant bits for the 22-bit Timemark Delay Counter down-count initialised value,

TIM_DEL, in conjunction with TIM_DEL_LO (see above). This is primarily a write-only register, but on reading the

register, the settings made by the previous Write can be observed.

Bit

No.

Mnemonic Description Reset

Value

R/W

7 TIM_DEL_TST

Reserved for Test purposes only.

0W

6 TIM_DEL_ENAB Toggles Timemark offset correction circuitry between:

'0' = Enable TIC Period Slewing logic, Disable M_CLK

from Timemark Delay Counter logic

'1' = Enable Timemark Delay Counter logic, Connect

M_CLK to Timemark Delay Counter. Disable TIC

Period Slewing logic.

0R/W

5:0 TIM_DEL[21:16]

6 MSBs of number of M_CLK clock cycles by which

TIC should be delayed before a Timemark Pulse is

produced, and completed.

Most Significant Bit = Bit 5.

0x00 R/W

Table 15.13 1PPS Timemark TIM_DEL_HI Register