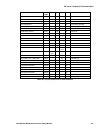

21: Timing Characteristics

198 GP4020 GPS Baseband Processor Design Manual

Parameter Min Max units Description and notes

Tbscl 15.6 - ns TCK low period

Tbsch 15.6 - ns TCK high period

Tbsis 5.0 - ns TDI,TMS setup to [TCr]

Tbsih 5.0 - ns TDI,TMS hold from [TCr]

Tbsoh 2.4 - ns TDO hold time

Tbsod - 25 ns TCr to TDO valid

Tbsr 25 - ns Reset period

Table 21.6 JTAG Timing parameters

Notes:

1) For correct data latching, the I/O signals (from the core and the pads) must be set-up and held with respect to

the rising edge of TCK in the CAPTURE-DR state of the INTEST and EXTEST instructions.

2) Assumes that the data outputs are loaded with the AC test loads (see AC parameter specification).