21: Timing Characteristics

GP4020 GPS Baseband Processor Design Manual 195

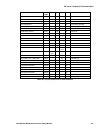

21.2 Memory Peripheral Controller (MPC) External Read & Write timing

parameters with SWait Control

Memory accesses with SWait control have default of one wait-state access, in addition to additional wait-states

triggered by an external SWait = High signal.

SDATA

NSOE

NSWE

NSCS

SADDR

BuILD_CLK

SWAIT

Default wait state External wait state Completion cycle

Read Transaction

Twh

Twsu

Figure 21.3 MPC Timing Diagram - External Memory Read Cycle with external Wait-State control

Parameter Min Max Unit Description and notes

Twsu 0 ns

SWait setup time before B

µILD CLK

Twh 7.5 ns

SWait hold time after B

µILD CLK

Table 21.2 Simulated SWait Timing parameters for MPC External Transactions

21.3 Direct Memory Access Controller (DMAC) single address transfer timing

BuILD_CLK

Dreq1,2

Dack1,2

n CLK

CYCLES

Tdreq

Tdreq_hold

TdackhTdack

Figure 21.4 DMAC timing: Single address transfer.