3: ARM7TDMI

TM

Microprocessor

GP4020 GPS Baseband Processor Design Manual 21

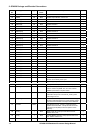

Mnemonic Instruction Action

ADC Add with carry Rd := Rn + Op2 + Carry

ADD Add Rd := Rn + Op2

AND AND Rd := Rn AND Op2

B Branch R15 := address

BIC Bit Clear Rd := Rn AND NOT Op2

BL Branch with Link R14 := R15, R15 := address

BX Branch and Exchange R15 := Rn, T bit := Rn[0]

CDP Coprocessor Data Processing (Coprocessor-specific)

CMN Compare Negative CPSR flags := Rn + Op2

CMP Compare CPSR flags := Rn - Op2

EOR Exclusive OR Rd := (Rn AND NOT Op2) OR (op2 AND NOT Rn)

LDC Load coprocessor from memory Coprocessor load

LDM Load multiple registers Stack manipulation (Pop)

LDR Load register from memory Rd := (address)

MCR Move CPU register to coprocessor register cRn := rRn {<op>cRm}

MLA Multiply Accumulate Rd := (Rm * Rs) + Rn

MOV Move register or constant Rd : = Op2

MRC Move from coprocessor register to CPU register Rn := cRn {<op>cRm}

MRS Move PSR status/flags to register Rn := PSR

MSR Move register to PSR status/flags PSR := Rm

MUL Multiply Rd := Rm * Rs

MVN Move negative register Rd := 0xFFFF FFFF EOR Op2

ORR OR Rd := Rn OR Op2

RSB Reverse Subtract Rd := Op2 - Rn

RSC Reverse Subtract with Carry Rd := Op2 - Rn - 1 + Carry

SBC Subtract with Carry Rd := Rn - Op2 - 1 + Carry

STC Store coprocessor register to memory address := CRn

STM Store Multiple Stack manipulation (Push)

STR Store register to memory <address> := Rd

SUB Subtract Rd := Rn - Op2

SWI Software Interrupt OS call

SWP Swap register with memory Rd := [Rn], [Rn] := Rm

TEQ Test bitwise equality CPSR flags := Rn EOR Op2

TST Test bits CPSR flags := Rn AND Op2

Table 3.1 Standard 32-bit ARM instruction set