3: ARM7TDMI

TM

Microprocessor

24 GP4020 GPS Baseband Processor Design Manual

System

& User

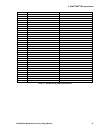

FIQ Supervisor Abort IRQ Undefined

R0 R0 R0 R0 R0 R0

R1 R1 R1 R1 R1 R1

R2 R2 R2 R2 R2 R2

R3 R3 R3 R3 R3 R3

R4 R4 R4 R4 R4 R4

R5 R5 R5 R5 R5 R5

R6 R6 R6 R6 R6 R6

R7 R7 R7 R7 R7 R7

SP SP_fiq * SP_svc* SP_abt * SP_irq * SP_und *

LR LR_fiq * LR_svc * LR_abt * LR_irq * LR_und *

PC PC PC PC PC PC

Table 3.5 Thumb State General Registers and Program Counter

CPSR CPSR CPSR CPSR CPSR CPSR

SPSR_fiq * SPSR_svc * SPSR_abt * SPSR_irq * SPSR_und *

Table 3.6 Thumb State Program Status Registers

* Indicates register is banked.

3.6 Low Power ARM7TDMI Sleep Mode

A feature of the Firefly MF1 ARM7TDMI, is a Sleep Coprocessor, which can be used to disable the clock to the

ARM7TDMI, but keep it enabled to other parts of the Firefly MF1. This is different to the F_SLEEP utility in the

Peripheral Control Logic block of the GP4020, as it allows all other Firefly blocks to remain operable while the

ARM7TDMI is halted.

The ARM7TDMI core does not inherently contain a low power sleep mode; however, the architecture does contain

a mechanism for instruction set extension through the coprocessor interface. Zarlink has taken advantage of this

interface to define a coprocessor instruction set implementing a low power operation (sleep) mode.

This coprocessor is assigned coprocessor number "3", and performs Coprocessor Data operations (CDP). In the

implementation contained within the Firefly MF1 micro-controller, one coprocessor instruction (“0”) is defined:

0 Suspend processor operation and halt processor clock until interrupt is received from any enabled

interrupt in the INTC block. Upon receipt of interrupt, execute an interrupt service routine, then resume the

normal flow of execution after the CDP instruction.

All other instructions for that coprocessor and all other coprocessor instruction types are reserved. The assembly

code for the SLEEP instruction is:

NOP

NOP

CDP p3,0,c0,c0,c0

; Firefly Arm7 Sleep enable, Coprocessor no. 3, Operation ‘0’

; The ARM CPU has now been halted. Other Masters may still operate.

; An interrupt to the ARM will reawaken the ARM.

NOP

NOP