TMS320VC5402

FIXEDĆPOINT DIGITAL SIGNAL PROCESSOR

SPRS079E – OCTOBER 1998 – REVISED AUGUST 2000

52

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

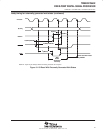

instruction acquisition (IAQ), interrupt acknowledge (IACK), external flag (XF), and TOUT timings

switching characteristics over recommended operating conditions for IAQ

and IACK

[H = 0.5 t

c(CO)

] (see Figure 25)

PARAMETER MIN MAX UNIT

t

d(CLKL-IAQL)

Delay time, CLKOUT low to IAQ low –1 3 ns

t

d(CLKL-IAQH)

Delay time, CLKOUT low to IAQ high –1 3 ns

t

d(A)IAQ

Delay time, address valid to IAQ low 1 ns

t

d(CLKL-IACKL)

Delay time, CLKOUT low to IACK low –1 3 ns

t

d(CLKL-IACKH)

Delay time , CLKOUT low to IACK high –1 3 ns

t

d(A)IACK

Delay time, address valid to IACK low 3 ns

t

h(A)IAQ

Hold time, IAQ high after address invalid –2 ns

t

h(A)IACK

Hold time, IACK high after address invalid –2 ns

t

w(IAQL)

Pulse duration, IAQ low 2H–2 ns

t

w(IACKL)

Pulse duration, IACK low 2H–2 ns

MSTRB

IACK

IAQ

A[19:0]

CLKOUT

t

d(A)IACK

t

d(A)IAQ

t

w(IACKL)

t

h(A)IACK

t

d(CLKL-IACKL)

t

w(IAQL)

t

h(A)IAQ

t

d(CLKL-IAQL)

t

d(CLKL-IACKH)

t

d(CLKL-IAQH)

Figure 25. IAQ and IACK Timings