TMS320VC5402

FIXEDĆPOINT DIGITAL SIGNAL PROCESSOR

SPRS079E – OCTOBER 1998 – REVISED AUGUST 2000

44

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

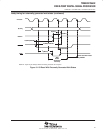

memory and parallel I/O interface timing (continued)

switching characteristics over recommended operating conditions for a

parallel I/O port write

(IOSTRB

= 0)

[H = 0.5 t

c(CO)

]

†

(see Figure 16)

PARAMETER MIN MAX UNIT

t

d(CLKL-A)

Delay time, CLKOUT low to address valid –2 3 ns

t

d(CLKH-ISTRBL)

Delay time, CLKOUT high to IOSTRB low –2 3 ns

t

d(CLKH-D)IOW

Delay time, CLKOUT high to write data valid H–5 H+8 ns

t

d(CLKH-ISTRBH)

Delay time, CLKOUT high to IOSTRB high –2 3 ns

t

d(CLKL-RWL)

Delay time, CLKOUT low to R/W low –1 3 ns

t

d(CLKL-RWH)

Delay time, CLKOUT low to R/W high –1 3 ns

t

h(A)IOW

Hold time, address valid after CLKOUT low 0 3 ns

t

h(D)IOW

Hold time, write data after IOSTRB high H–3 H+7 ns

t

su(D)IOSTRBH

Setup time, write data before IOSTRB high H–7 H+1 ns

t

su(A)IOSTRBL

Setup time, address valid before IOSTRB low H–2 H+2 ns

†

Address and IS

timings are included in timings referenced as address.

IS

R/W

IOSTRB

D[15:0]

A[19:0]

CLKOUT

t

d(CLKH-ISTRBH)

t

h(A)IOW

t

h(D)IOW

t

d(CLKH-D)IOW

t

d(CLKH-ISTRBL)

t

d(CLKL-A)

t

d(CLKL-RWL)

t

d(CLKL-RWH)

t

su(A)IOSTRBL

t

su(D)IOSTRBH

NOTE A: A[19:16] are always driven low during accesses to I/O space.

Figure 16. Parallel I/O Port Write (IOSTRB = 0)