115

APPENDICES

A

Appendix 4 Special Register (SD) for MELSECNET/H (MELSECNET/10 Mode) Remote I/O Station

*1 This applies to Universal model QCPUs except for the Built-in Ethernet port QCPU.

(2) System information

SD105

CH1

transmission

speed setting

(RS-232)

Stores a

transmission

speed set in

GX Developer.

96: 9600bps, 192: 19.2kbps,

384: 38.4kbps, 576: 57.6kbps,

1152: 115.2kbps

The data of the RS-232 connection is used for any other connection.

(When an external device is not connected, the default is 1152).

SNew

Qn(H)

QnPH

QnPRH

QnU

*1

Rem

No. Name Meaning Explanation

Set by

(When Set)

Corres-

ponding

ACPU

D9

Corres-

ponding

CPU

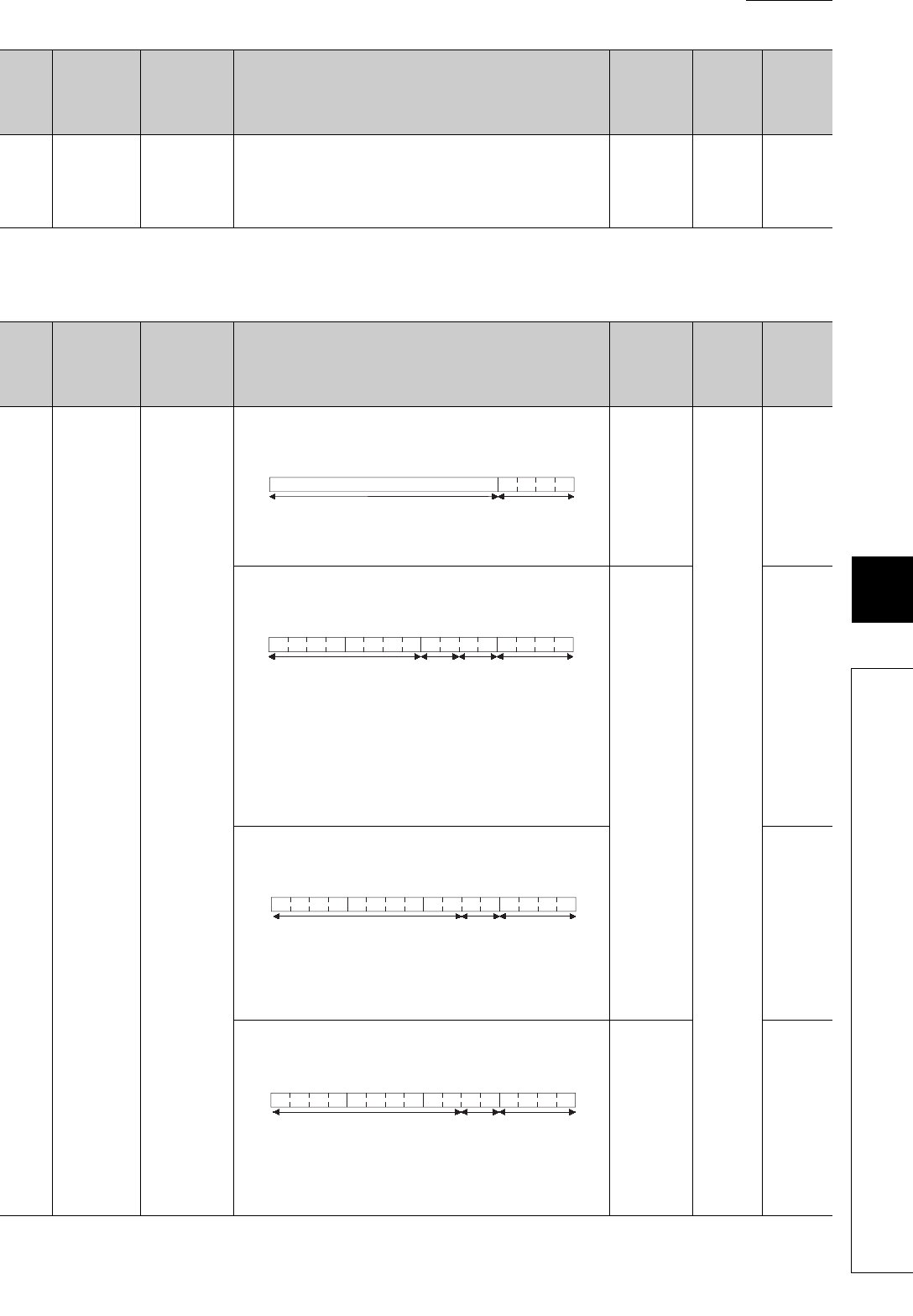

SD200

Status of

switch

Status of CPU

switch

This register stores the status of the remote I/O module switch in the

following bit pattern.

1) Remote I/O module switch status

Always 1: STOP

S

(Always)

New

Rem

This register stores the status of the CPU module switches in the

following bit pattern.

1) CPU switch status

0: RUN

1: STOP

2: L.CLR

2) Memory card switch: Always OFF

3) DIP switch

B8 through B12 correspond to SW1 through SW5 of system

setting switch 1. 0: OFF, 1: ON. BD through BF are empty.

S

(Every END

processing)

Qn(H)

QnPH

QnPRH

This register stores the status of the CPU module switches in the

following bit pattern.

1) CPU switch status

0: RUN

1: STOP

2) Memory card switch: Always OFF

Q00J/

Q00/Q01

This register stores the status of the CPU module switches in the

following bit pattern.

1) CPU switch status

0: RUN

1: STOP

2) Memory card switch: Always OFF

S

(when RUN/

STOP/

RESET

switch

changed)

QnU

No. Name Meaning Explanation

Set by

(When Set)

Corres-

ponding

ACPU

D9

Corres-

ponding

CPU

B15 B4 B3 B0

1)

Empty

B15 B12B11 B8 B7 B4B3 B0

1)2)

Empty

3)

B15 B6 B4 B3 B0

1)2)

Empty

B5

B15 B6 B4 B3 B0

1)2)

Empty

B5