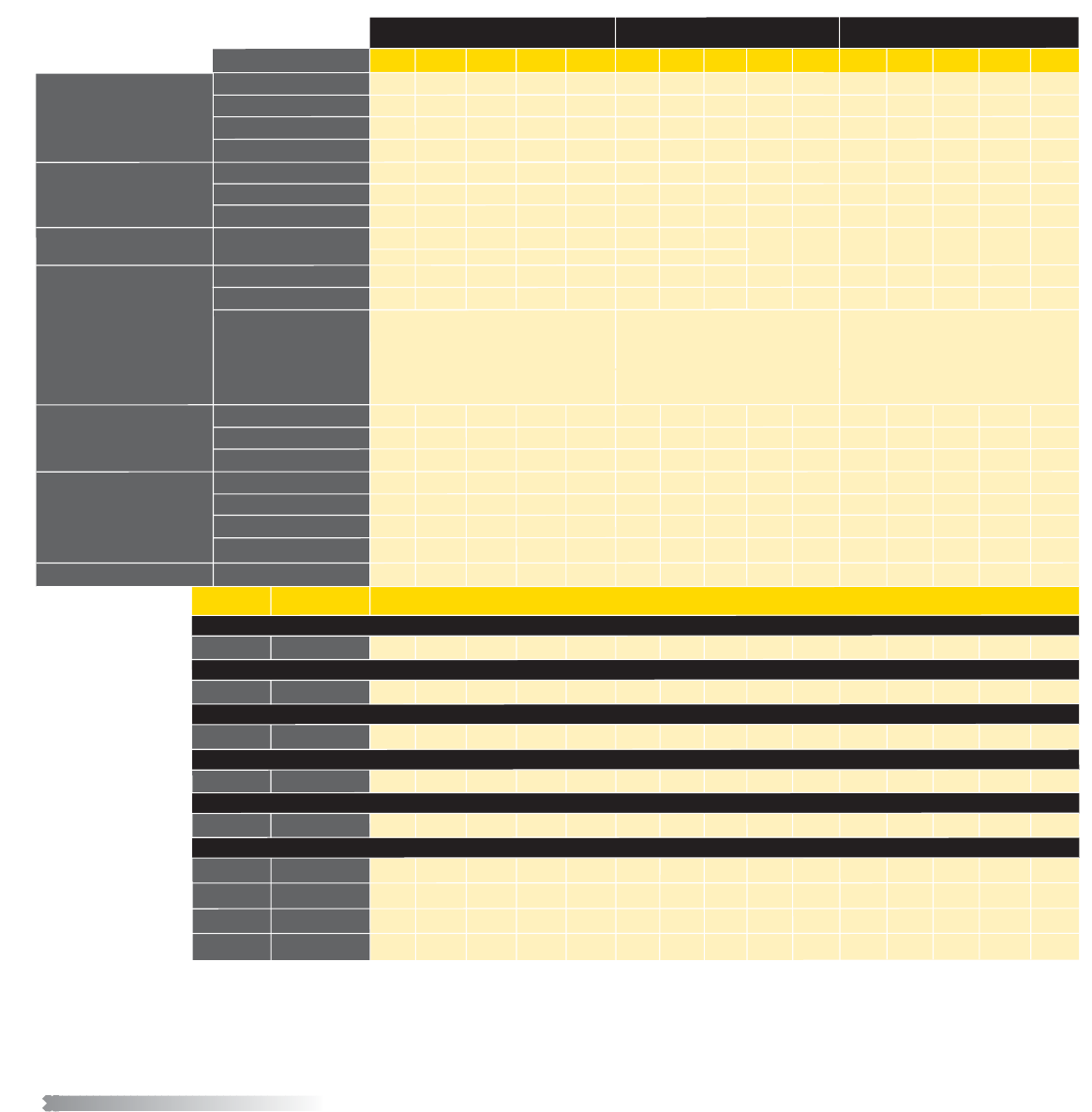

XILINX AUTOMOT IVE

DEVICES

1. System Gates include 20%-30% of CLBs used as RAMs. 2. Each slice comprises two 4-input logic function generators (LUTs), two storage elements, wide-function multiplexers, and carry logic.

Integrated in the DSP48A slices (Advanced Multiply Accumulate element). 4. Temperature Range Automotive I (T

j

= -40°C to +100°C); Automotive Q (T

j

= -40°C to +125°C)

Notes:

Part Number

Logic Cells

CLB Flip-Flops

VQG100 16 x 16 mm

Block RAM Blocks

Total Block RAM (Kbits)

Digital Clock Managers

(DCMs) Spartan-3, (DLLs) Spartan-IIE

Maximum Single Ended I/Os

Maximum Differential I/O Pairs

I/O Standards Supported

Dedicated Multipliers

DSP48A Slices

Device DNA Security

Temperature Range

(4)

Speed Grade

Maximum Distributed RAM (Kbits)

RoHS (Pb-free)

XA Released

Configuration Memory Bits (Mbits)

Slices

(2)

Logic Resources

Memory Resources

Clock Resources

I/O Resources

Embedded Hard

IP Resources

Configuration

Miscellaneous

TQG144 22 x 22 mm

PQG208 30.6 x 30.6 mm

FTG256 17 x 17 mm

FGG456 23 x 23 mm

FGG676 27 x 27 mm

System Gates

(1)

102 102

182182182

Spartan-IIE

XA2S50E

768

50K

1,728

1,536

8

32

4

102

28

—

—

—

I, Q

-6

XA2S100E

1,200

100K 150K 200K

2,700

2,400

10

40

4

102

28

—

—

—

I, Q

-6

XA2S150E XA2S200E

1,728

3,888

3,456

12

48

4

182

83

LVTTL, LVCMOS25, LVCMOS18, HSTL Class I, HSTL Class III,

HSTL Class IV, PCI 3.3V 32 - 33MHz, PCI-X 3.3V, SSTL3 Class I,

SSTL3 Class II, SSTL2 Class I, SSTL2 Class II,

AGP-2x, CTT, LVDS, Bus LVDS, LVPECL25 & 33

—

—

—

I, Q

-6

2,352

5,292

4,704

24 37 54 73

14

56

4

182

83

—

—

—

I, Q

-6

No No No No

Yes Yes Yes Yes

0.6 0.9 1.1 1.4

300K

XA2S300E

3,072

6,912

6,144

96

16

64

4

182

83

—

—

—

I, Q

-6

No

Yes

1.9

XA3S50

Spartan-3

XA3S200 XA3S400 XA3S1000 XA3S1500

768 1,920 3,584 7,680 13,312

50K 200K 400K 1000K 1500K

1,728 4,320 8,064 17,280 29,952

1,536 3,840 7,168 15,360 26,624

412162432

72 216 288 432 576

24444

124 173 264 333 487

56 76 116 149 221

412162432

63 63

—————

—————

I, Q I, Q I, Q I, Q I

-4 -4 -4 -4 -4

12 30 56 120 208

Yes Yes Yes Yes Yes

Yes Yes Yes Yes Yes

0.4 1.0 1.7 3.2 5.2

97

124 141 141

173 173 173

264 333 333

487

LVTTL, LVCMOS33, LVCMOS25, LVCMOS18, LVCMOS15,

LVCMOS12, GTL, GTL+, HSTL15 Class I, HSTL15 Class III,

HSTL18 Class I, HSTL18 Class II, HSTL18 Class III, PCI 3.3V

32/64bit 33MHz, SSTL2 Class I, SSTL2 Class II, SSTL18

Class I, Bus LVDS, LDT (ULVDS), LVDS_ext, LVDS25 & 33,

LVPECL25, RSDS25

66

158

66

158

172 190 190

FGG484 23 x 23 mm

376

FGG400 21 x 21 mm

304 304

108 108

CPG132 8 x 8 mm

839292

Spartan-3E

XA3S100E

960

100K

2,160

1,920

4

72

2

108

40

4

—

—

I, Q

-4

XA3S250E

2,448

250K

5,508

4,896

12

216

4

172

68

12

—

—

I, Q

-4

XA3S500E

4,656

500K 1200K 1600K

10,476

9,312

20

360

4

190

77

20

—

—

I, Q

-4

XA3S1200E XA3S1600E

8,672

19,512

17,344

28

504

8

304

124

LVTTL, LVCMOS33, LVCMOS25, LVCMOS18, LVCMOS15,

LVCMOS12, HSTL18 Class I, HSTL18 Class III, PCI 3.3V

32/64bit 33MHz, PCI-X 3.3V, SSTL2 Class I, SSTL18 Class I,

Bus LVDS, LVDS25, LVPECL25, Mini-LVDS25, RSDS25

28

—

—

I, Q

-4

14,752

33,192

29,504

15 38 73 136 231

36

648

8

376

156

36

—

—

I, Q

-4

Yes Yes Yes Yes Yes

Yes Yes Yes Yes Yes

0.6 1.4 2.3 3.8 6.0

Package Area Maximum User I/Os

VQFP Packages (VQ): very thin QFP (0.5 mm lead spacing)

Chip Scale Packages (CP): wire-bond chip-scale BGA (0.5 mm ball spacing)

TQFP Packages (TQ): thin QFP (0.5 mm lead spacing)

PQFP Packages (PQ): wire-bond plastic QFP (0.5 mm lead spacing)

FGA Packages (FT): wire-bond fine-pitch thin BGA (1.0 mm ball spacing)

FGA Packages (FG): wire-bond fine-pitch BGA (1.0 mm ball spacing)

FPGAs

Automotive

Auto.Brochure_Final.qxd 12/19/07 9:19 AM Page 14