VEHICLE NETWORKING

Automotive

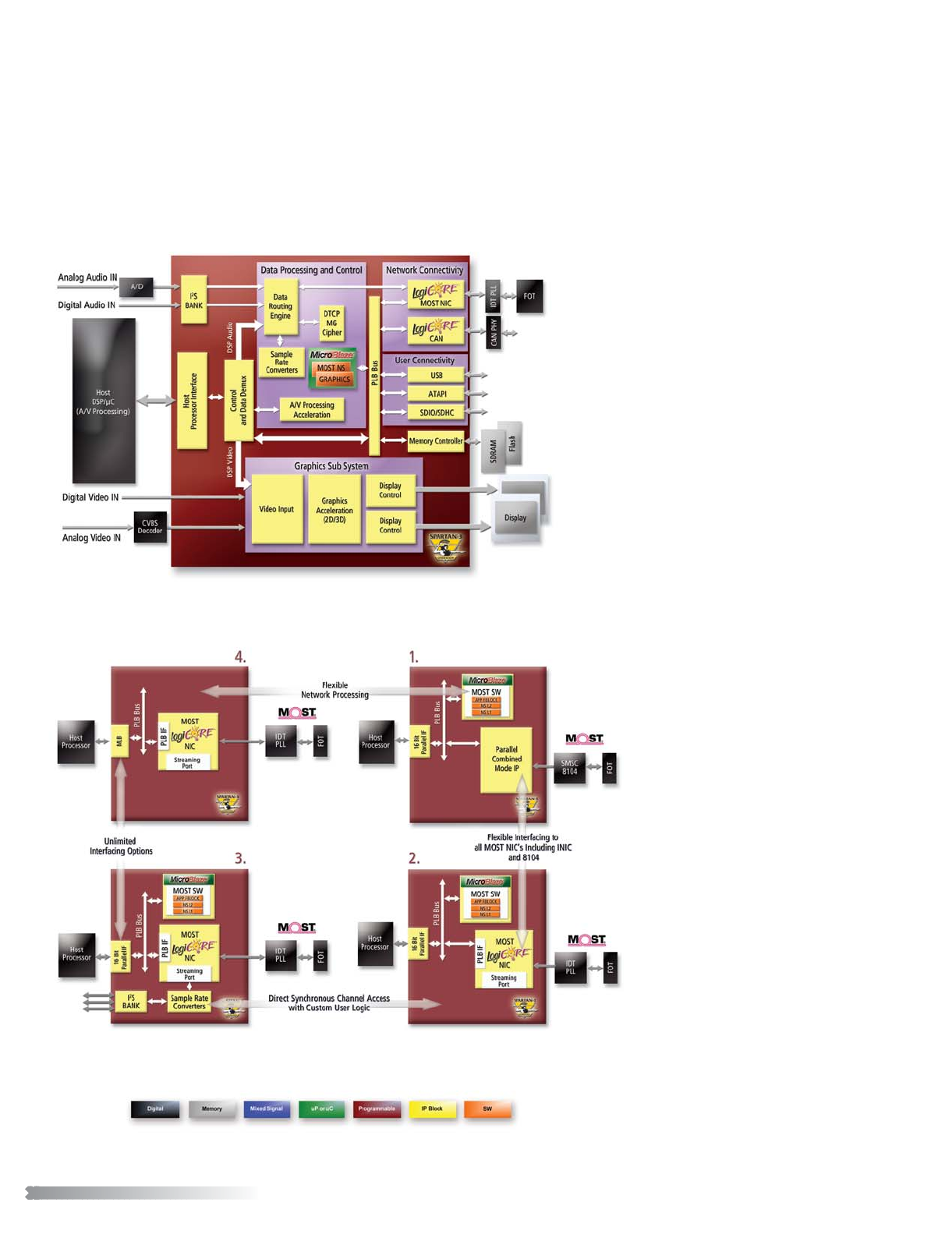

This super-set block diagram of an infotainment rear-seat

entertainment application shows a possible set-up based on

the combination of a host or digital signal processor (DSP)

together with an FPGA. In this example, the FPGA acts as

a companion chip to the host, providing multiple functions,

such as audio/video processing acceleration, a graphics

sub-system, and different user and vehicle networking

connections, such as CAN and MOST.

The following overview outlines four architectural options

showing how various components within the Xilinx solution

for MOST, including the MOST Network Interface Controller

(NIC), can be utilized to realize efficient system architectures.

There are many possible combinations that are not constrained

by fixed or predetermined interfaces, but can be

freely defined based on the desired overall system

architecture.

1. Off-loading the host processor by utilizing

the MicroBlaze processor to run the full

MOST Network Services software stack

along with OEM-specific FBlocks and High-

Level-Protocols in conjunction with the

OS8104 (PCM IP) or OS81050 (MLB IP).

2. Utilization of available LogiCORE IP to

completely eliminate the need for an external

MOST network controller.

3. Addition of direct access to the synchronous

MOST channels to perform pre- or post-

processing of incoming or outgoing data in

FPGA hardware without the need for any

software overhead.

4. Connectivity to a wide range of different

host interfaces.

Flexible MOST Architecture

_

your design, your way

Auto.Brochure_Final.qxd 12/19/07 9:19 AM Page 10